In this paper, through the analysis of the encoding and decoding process of low density check (LDPC) code, a joint design method of LDPC codec based on FPGA is proposed. This method makes the encoder and decoder share the same check calculation circuit. And the same RAM memory block is reused, which effectively reduces the consumption of hardware resources. The method is suitable for coding and decoding using a check matrix, and is applicable not only to a fully parallel codec structure, but also to a partially parallel structure that is widely used at present, and can use a sum product, a minimum sum, and the like. Decoding algorithm. This method is used to jointly design the codec of partial parallel structure of two different LDPC codes. The implementation results on Xilinx XC4VLX80 FPGA show that the designed encoder and decoder can work in parallel and occupy only slightly more. The hardware resources of a single decoder, the proposed design method can effectively reduce the system's hardware resource requirements without reducing the throughput.

1 IntroductionIn digital communication systems, forward error correction coding (FEC) technology can greatly improve the reliability of data transmission. Among them, LDPC code has been used by digital satellite broadcasting (DVBS2), wireless local area network (WLAN) and global microwave interconnection (WIMAX) due to its excellent error correction performance, low decoding complexity and parallelizable decoding structure. ) and other communication standards adopted.

How to implement high-speed LDPC codec on large-scale integrated circuits has always been a focus of LDPC code application research. In theory, the LDPC code decoder with full parallel structure can be realized according to all the nodes and edges in the bipartite graph, but with the increase of code length, too high wiring complexity and huge resource demand will lead to full parallel structure. The decoder is difficult to implement. Although the serial structure can reduce the consumption of hardware resources, the storage space required by the decoder increases rapidly with the increase of the code length, and the lower decoding throughput usually cannot meet the requirements of practical applications. In 2001, Kou et al. [1] proposed a quasi-cyclic structure LDPC code. Due to the quasi-cyclic nature of the check matrix, the decoder can adopt a partial parallel structure.

The line is implemented so that the long code based high throughput LDPC code decoder is put to practical use. At present, the research work of partial parallel structure QC-LDPC decoder has been fully developed. Several effective FPGA-based decoder implementation methods are given in [2-8]. In the implementation of the encoder, if the generator matrix coding is directly used, the algorithm complexity will increase with the increase of the code length at the square speed. In 2001, Richardson et al. [9] proposed a simplified coding algorithm, but its The amount of storage and computation required is still too large. Since then, scholars have proposed some structured coding methods, one of which is to design the generation matrix and also have quasi-cyclical LDPC codes, which are encoded by the generator matrix. The coding circuit of the method is given in [10]. The method is to use a special structure of a quasi-cyclic check matrix for encoding. For example, IEEE 802.16e (WiMAX), IEEE 802.11n (WLAN) and the like use a bi-diagonal quasi-cyclic check matrix for encoding. Structure, literature [11] proposed a fast recursive coding algorithm and its parallel hardware implementation architecture. However, the existing LDPC codec design methods are designed solely for encoders or decoders, and each optimizes its throughput and FPGA resources. The actual application systems are mostly full-duplex communication systems, and the system requires an encoder. Both the decoder and the decoder work at the same time. The separate design will make the hardware resources of the encoder and the decoder cannot be effectively multiplexed, resulting in low utilization of FPGA resources.

This paper proposes a joint design method for encoder and decoder for IEEE 802.16e, IEEE 802.11n and other proposed LDPC codes. This method enables the encoder to use the decoder to calculate the idle calculation circuit during vertical operation. Encode. In the proposed implementation structure, the data to be encoded, the data to be decoded and the decoded codeword share the same memory block, and each processing unit of the codec shares the same group address information, which effectively reduces the requirement of the hardware resources of the codec system.

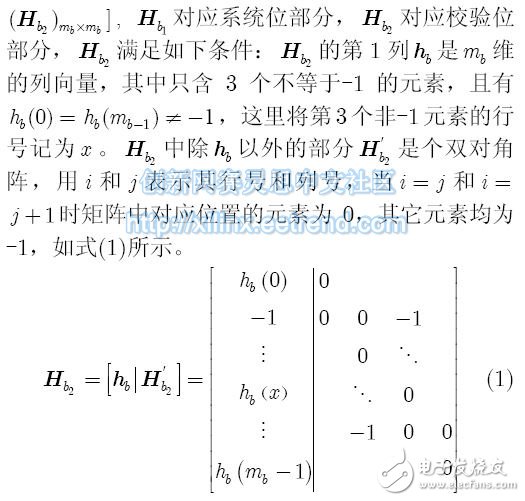

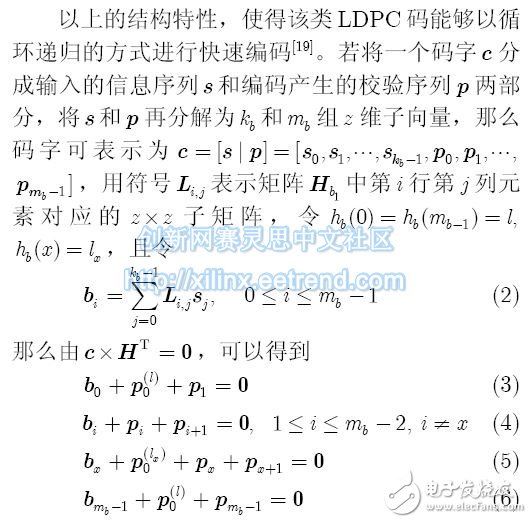

2 H matrix based LDPC coding

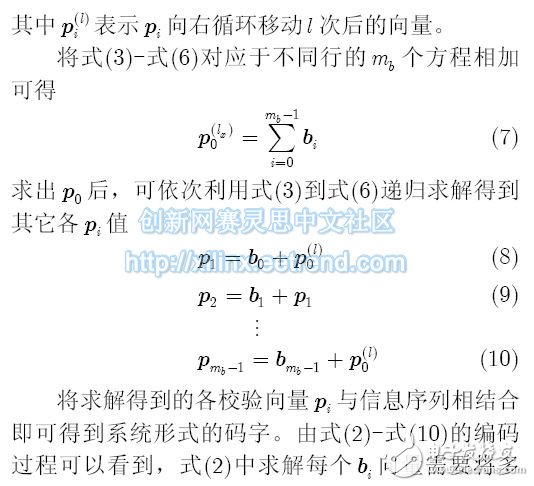

The results of multiplying the matrix by the vector are added, and a total of mb bi vectors need to be solved. Even if the matrix multiplication can be replaced by the cyclic shift of the vector due to the structural characteristics of the matrix, the calculation amount is still large. The other formulas are the sum of 2~3 vectors, and the calculation amount is actually less. Therefore, the computational complexity of the whole encoder is mainly concentrated in equation (2). By analyzing the equation (2), bi is actually obtained by adding the information bits corresponding to each bit of the H matrix to each bit. Obviously, if the check digits of the codeword sequence are all set to zero, the H matrix is ​​used to solve the adjointness. Then, the resulting syndrome is equivalent to bi. Therefore, it is possible to utilize the existing and idle check calculation circuit in the system, and multiplex it into the code of the information bits by calculating the syndrome after the check position is zero. The codec resource reuse scheme of this paper is designed by using the idea of ​​this verification calculation circuit coding.

Solar Power System Accessories

Solar Power System Accessories,Solar System Accessories,Solar Installation Kit,Solar Battery Kit

SUZHOU DEVELPOWER ENERGY EQUIPMENT CO.,LTD , https://www.fisoph-power.com